# ANALYTICAL STUDY OF MOS DEVICE FOR LEAKAGE REDUCTION IN LOW POWER CIRCUIT

# THESIS

submitted in fulfillment of the requirement of the degree of

# **DOCTOR OF PHILOSOPHY**

to

# J.C.BOSE UNIVERSITY OF SCIENCE & TECHNOLOGY, YMCA, FARIDABAD (Haryana)

by

**PRASHANT KUMAR** Registration No: YMCAUST/Ph20/2011

Under the Supervision of

PROF. MUNISH VASHISHATH PROFESSOR, EE DEPARTMENT JCBUST, YMCA, Faridabad PROF. P.K. BANSAL FORMER PRINCIPAL MIMIT, Malout, Punjab

Department of Electronics Engineering Faculty of Engineering and Technology J.C. Bose University of Science & Technology, YMCA, Faridabad Sector-6, Mathura Road, Faridabad, Haryana, India

**NOVEMBER 2021**

# DECLARATION

I hereby declare that this thesis entitled "ANALYTICAL STUDY OF MOS DEVICE FOR LEAKAGE REDUCTION IN LOW POWER CIRCUIT" by PRASHANT KUMAR being submitted in fulfillment of the requirements for the Degree of Doctor of Philosophy in ELECTRONICS ENGINEERING under FACULTY OF ENGINEERING & TECHNOLOGY, is a bonafide record of my original work carried out under joint guidance and supervision of DR.MUNISH VASHISHATH, PROFESSOR (ELECTRONICS ENGINEERING), J. C. BOSE UNIVERSITY OF SCIENCE & TECHNOLOGY, YMCA, FARIDABAD and DR. P. K. BANSAL, FORMER PRINCIPAL, MIMIT MALOUT, PUNJAB and has not been presented elsewhere.

I further declare that the thesis does not contain any part of any work which has been submitted for the award of any degree, either in this university or in any other university.

> (Prashant Kumar) YMCAUST /PH20/2011

# CERTIFICATE

This is to certify that the thesis entitled, "ANALYTICAL STUDY OF MOS DEVICE FOR LEAKAGE REDUCTION IN LOW POWER CIRCUIT" by PRASHANT KUMAR, being submitted in fulfillment of the requirement for the Degree of Doctor of Philosophy in ELECTRONICS ENGINEERING under Faculty of Engineering & Technology, J. C. Bose University of Science & Technology, YMCA, Faridabad, during the academic year 2021-22, is a bonafide record of work carried out under our joint guidance and supervision.

We further declare that to the best of our knowledge, the thesis does not contain any part of any work which has been submitted for the award of any degree, either in this university or in any other university.

# **Prof. Munish Vashishath**

Department of Electronics Engineering, J.C. Bose University of Science & Technology, YMCA, Faridabad **Prof. P.K. Bansal** Former Principal MIMIT, Malout, Punjab

Dated:

First of all, I sincerely acknowledge my gratitude to **ALMIGHTY** whose blessings have bestowed in me the will power and confidence to carry out my project. It is both an elevating and humbling experience to have the opportunity to acknowledge all the peoples involved in this thesis work.

I have a great pleasure to express my deep sense of respect and sincere gratitude to my supervisor *Prof. (Dr.) Munish Vashishath*, Professor, Electronics Engineering Department, J. C. Bose University of Science & Technology, YMCA, Faridabad, Haryana, for his guidance, motivation, and inspiration. He has been my inspiration as I hurdle all the obstacles in the completion of this research work. His encouragement and attention in every stage of my research work provided me with the spirit to complete this research.

I would also like to give my sincere thanks to my co-supervisor, *Prof. (Dr.) P. K. Bansal*, Former Principal, MIMIT Malout, Punjab, for his guidance, motivation, and inspiration. His continuous support and care on my work and career is simply unforgettable.

I also wish to express my sincere gratitude to *Dr. Pradeep Dimri*, Chairperson, Electronics Engineering Department, J. C. Bose University of Science & Technology, YMCA, Faridabad, Haryana for her sincerely help and providing me the necessary research facilities for the completion of the work.

I am grateful to *Prof. M. L. Aggarwal*, Dean (Engineering and Technology) and *Prof. Rajesh Ahuja*, Dean (R&D), J. C. Bose University of Science & Technology, YMCA, for their support and encouragement during my course of study.

I am very much thankful to *Dr. Neeraj Gupta*, AMITY University, Gurugram, who has been a constant support to me and helped me for understanding the complex mathematical modeling during my research work.

I am also thankful to the all faculty members and staff of Electronics Engineering Department of J. C. Bose University of Science & Technology, YMCA, Faridabad for their continuous support and co-operation.

Though inept, I would like to express my deep gratitude to my parents, for being supportive, understanding, patient, and for having shaped me into who I am. They have always encouraged my academic endeavour which is my greatest motivation in the study.

I also express my deep appreciation to my wife *Dr. Raj Kumari* and loving son *Aaradhay*, whom constant inspiration, patience, understanding and moral support have greatly contributed to the realization of this work.

I feel indebted to all well-wishers, whose names remain unmentioned but who have never retraced back from helping me whenever the need arose.

Prashant Kumar

# ABSTRACT

The transistor is the elementary unit of all the electronic systems. The advancements in the performance of these systems have changed the world. In the recent years, the development of small, computationally efficient and portable system is mainly due to the miniaturization of semiconductor devices which, in turn, are heavily dependent on the improvement in the Metal Oxide Semiconductor Field-Effect Transistor (MOSFET) technology. The invention of MOSFET gave the quantum leap to the semiconductor components. In order to upgrade, this device has to be regularly scaled to small dimensions. The enhanced speed of operation, less size and lower power consumptions from predecessor are two other key parameters for next-generation semiconductor devices. With continuous scaling, the dimension of MOSFET has reached into nano-meter regime.

The performances of a scaled MOSFET degrade considerably due to the unpredictable electrical behaviour which is known as Short Channel Effects (SCEs). These effects arise mainly due to weakened control of gate over the channel. The Short Channel Effects leads to increase sub-threshold leakage current which affects the device characteristics. These short channel effects have become obstacle for further scaling of the devices while maintaining a good performance. Hence, it is required to improve the MOSFET technology by identifying the innovative approach to meet the expected performance with the upcoming scaling. It is very challenging to get the acceptable gate control over the channel with the planar MOSFET structures. Many novel device structures have been presented in literature to address the challenge of Short Channel Effects (SCEs). The Silicon-on-Insulator (SOI) technology has been utilized as the CMOS technology in the last decade due to the advantages of speed, packing density, excellent resistance to radiation and most importantly the immunity to Short Channel Effects. In addition to the effective suppression of short channel effects, SOI MOSFET gives excellent current drive capability and these structures are compatible with conventional CMOS processes. SOI device composed of a buried oxide layer on which a silicon layer is deposited in which source and drain are formed. SOI structure is dielectrically isolated to each other and from substrate layer. A higher packing density can be achieved in SOI devices due to inbuilt isolation from neighbouring transistors in SOI devices. The presence of buried oxide layer makes SOI free from the latch-up phenomenon. Hence for predefined power consumption, a highly dense and faster circuit can be fabricated using SOI devices process.

The continued investigation for an alternative MOSFET to have better electrical characteristics led to the introduction of new materials and concepts to overcome the Short Channel Effects (SCEs). The usage of high-k materials as gate dielectric provides the advantages of reduced parasitic capacitances and low off current.  $HfO_2$  as high-k material was used for analysis in the present work due to its better properties compared to other high-k materials. Due to the advantages offered by high-k materials,  $HfO_2$  is used as dielectric materials for every MOSFET structure reported in the present research work by replacing/stacking with SiO<sub>2</sub>.

The planner MOSFET structures having single gate at very small dimension are incapable to have good control of gate over the channel. Hence the multi-gate approach is good option for further scaling of the planner MOSFET. The design of such multi-gate structure may be complex but enhance the performance of the device by reducing the Short Channel Effects. The multi-gate structure including Double Gate, Triple Gate and Cylindrical Gate All Around Structures provide better control of channel and suppression of Short Channel Effects. Among all of these Cylindrical Gate All Around MOSFET structure offers the best performance. In this structure, the channel is completely surrounded by the gate. This structure provides better gate control and enhances the current driving capability of the device.

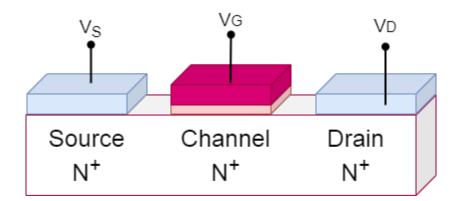

With MOSFET device technology reaching under 10nm, the formation of ultra-thin junction requires costly and sophisticated fabrication process. Hence, a device where junction and individual source/drain regions formation is not required will prove to be a better solution to the complex problem of scaling and fabrication. The device which has the same material from source to drain is called Junctionless Field Effect Transistor (JLFET). The operation of the device depends upon the work function difference between the gate metal and silicon. The device has CMOS functionality with the attributes of no junction. The JLFET was found to have less leakage current than conventional MOSFET structures. This device has same type and concentration of doping throughout the device active region. The device shows efficient results in suppressing the short channel effects. In the present research work the analytical

modeling of the JLFET has been carried out by solving the Poisson's Equation using Parabolic Approximation Technique. This analytical model is verified with the simulation results obtained from the Device Simulator Atlas from Silvaco.

The dual-material/triple material gates on MOSFET structure offers an alternative way of simultaneous short channel effects suppression and improved device performance by careful control of the material work-function.

The present work includes a superior device in which all the device improvement approaches like Gate Engineering, Channel Engineering, Gate Work-Function Engineering and Device Engineering have been applied. The "Stacked Dielectric Triple Material Cylindrical Gate All Around Junctionless Field Effect Transistor (SD-TM-CGAA-JLFET)" structure have been presented on the basis of above device improvement approaches. The stacked dielectric structure minimizes the gate leakage and improves the carrier transportation efficiency in the channel. Triple materials gate composed of metal gates made up of three different metals having different workfunction which results in the suppression of short channel effects. The Cylindrical Gate All Around structure provides very good gate control over the channel. The JLFET offers a simple structure which again provides better short channel effects immunity and negligible off current. The SD-TM-CGAA-JLFET structure was simulated and analytically modelled for the sub-threshold current which is the prime objective of this research work.

The suitability of SD-TM-CGAA-JLFET for circuit applications is analyzed with the help of the CMOS inverter circuit and various characteristics of the inverter were analysed. The excellent agreement is found between the analytical and simulated results. The static power dissipation of CMOS inverter with SD-TM-CGAA-JLFET structure as NMOS and PMOS was found to be 5 times less than the static power of CMOS inverter designed using SOI-based Double gate Junctionless transistor of comparable dimension. From the analysis, it is found that SD-TM-CGAA-JLFET device will be a better alternative for the nanoscale MOSFET device.

# **TABLE OF CONTENTS**

| Candidate's Declaration | i    |

|-------------------------|------|

| Certificate             | ii   |

| Acknowledgement         | iii  |

| Abstract                | v    |

| Table of Contents       | viii |

| List of Tables          | xiii |

| List of Figures         | xiv  |

| List of Symbols         | xvii |

|                         |      |

# **CHAPTER – I INTRODUCTION**

| 1.1  | PREAN  | MBLE 1                                          |    |  |  |

|------|--------|-------------------------------------------------|----|--|--|

| 1.2  | MOSFI  | ETS                                             | 3  |  |  |

|      | 1.2.1  | Construction of the MOSFETS                     | 4  |  |  |

|      | 1.2.2  | MOSFET Operation                                | 5  |  |  |

|      |        | 1.2.2.1 Cut- off mode                           | 6  |  |  |

|      |        | 1.2.2.2 Triode region or Linear mode            | 6  |  |  |

|      |        | 1.2.2.3 Saturation mode                         | 7  |  |  |

|      | 1.2.3  | Distinguished Features of MOSFET                | 7  |  |  |

| 1.3  | ITRS R | COADMAP FOR SEMICONDUCTORS                      | 8  |  |  |

| 1.4  | TECHN  | NOLOGY TRENDS IN POWER DISSIPATION              | 8  |  |  |

| 1.5  | POWE   | R DISSIPATION IN CMOS CIRCUITS                  | 10 |  |  |

|      | 1.5.1  | Dynamic Power Dissipation                       | 10 |  |  |

|      | 1.5.2  | Short Circuit Power Dissipation                 | 10 |  |  |

|      | 1.5.3  | Static Leakage Power Dissipation                | 11 |  |  |

|      |        | 1.5.3.1 Static Leakage Current                  | 11 |  |  |

| 1.6  | DESIG  | GNING FOR LOW POWER13                           |    |  |  |

| 1.7  | POWE   | R MINIMIZATION TECHNIQUES                       | 14 |  |  |

|      | 1.7.1  | Supply Voltage Scaling                          | 14 |  |  |

|      | 1.7.2  | Reduction of Capacitance                        | 14 |  |  |

|      | 1.7.3  | Better Design Techniques Employment             | 14 |  |  |

|      | 1.7.4  | Better Power Management Approaches              | 15 |  |  |

| 1.8  | MOOR   | E'S LAW                                         | 15 |  |  |

| 1.9  | MOSFI  | ET SCALING                                      | 16 |  |  |

|      | 1.9.1  | Constant Field Scaling                          | 16 |  |  |

|      | 1.9.2  | Constant Voltage Scaling                        | 17 |  |  |

|      | 1.9.3  | Generalized Scaling                             | 17 |  |  |

|      | 1.9.4  | Modern Scaling                                  | 18 |  |  |

| 1.10 | LIMIT  | ATIONS OF SCALING                               | 18 |  |  |

|      | 1.10.1 | Drain Induced Barrier Lowering (DIBL)           | 19 |  |  |

|      | 1.10.2 | Velocity Saturation                             | 20 |  |  |

|      | 1.10.3 | Impact Ionization                               | 20 |  |  |

|      | 1.10.4 | Channel Length Modulation                       | 21 |  |  |

|      | 1.10.5 | Surface/Channel Scattering                      | 21 |  |  |

|      | 1.10.6 | Hot Carrier Effect                              | 22 |  |  |

|      | 1.10.7 | Source /Drain Parasitic Resistance/Capacitances | 23 |  |  |

|      | 1.10.8 | Mobility Degradation                            | 23 |  |  |

|      | 1.10.9 | Fringing Field Effects                          | 24 |  |  |

|      | 1.10.10 Sub-threshold Conduction                     | 24   |

|------|------------------------------------------------------|------|

|      | 1.10.11 Threshold Voltage Roll-off                   | 24   |

| 1.11 | REDUCTION OF SHORT CHANNEL EFFECTS                   | 25   |

|      | 1.11.1 Gate Dielectric Engineering                   | 25   |

|      | 1.11.2 Channel Doping                                | 26   |

|      | 1.11.3 Gate Metal Engineering                        | 27   |

| 1.12 | ALTERNATIVE MOSFET DEVICE STRUCTURES                 | 28   |

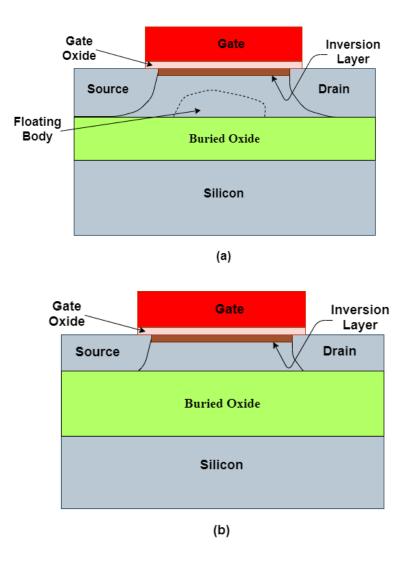

|      | 1.12.1 Silicon Over Insulator (SOI)                  | 28   |

|      | 1.12.1.1 Partially Depleted (PD) devices             | 28   |

|      | 1.12.1.2 Fully Depleted (FD) devices                 | 29   |

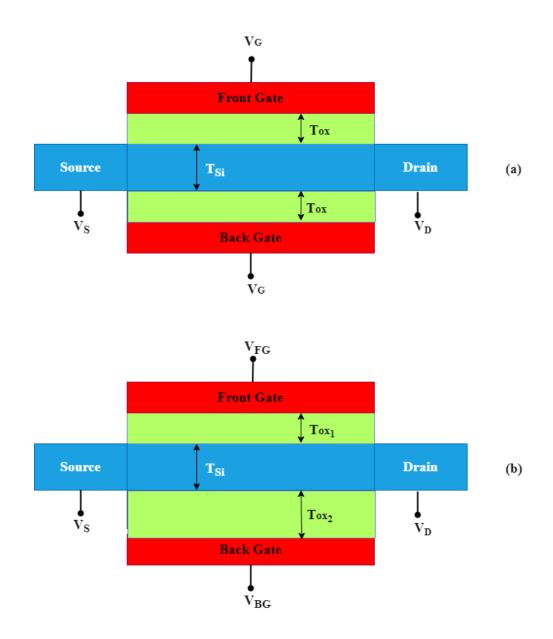

|      | 1.12.2 MULTIGATE MOSFET                              | 30   |

|      | 1.12.2.1 Double Gate MOSFET                          | 30   |

|      | 1.12.3 Junctionless Field Effect Transistors (JLT)   | 32   |

|      | 1.12.4 Other Alternative Device Structures           | 33   |

| 1.13 | TECHNOLOGY COMPUTER-AIDED DESIGN (TCAD)              | 33   |

|      | UTILIZATION                                          |      |

| 1.14 | DEVICE MODELING                                      | 34   |

|      | 1.14.1 MOSFET Device Modelling                       | 35   |

|      | 1.14.2 Analytical Models                             | 35   |

| 1.15 | RESEARCH OBJECTIVE                                   | 36   |

| 1.16 | RESEARCH METHODOLOGY                                 | 36   |

| 1.17 | THESIS ORGANISATION                                  | 37   |

| CHA  | APTER –II LITERATURE REVIEW                          |      |

| 2.1  | INTRODUCTION                                         | 39   |

| 2.2  | GATE ENGINEERING                                     | 40   |

|      | 2.2.1 Threshold Voltage Characteristics              | 41   |

|      | 2.2.2 Sub-threshold Characteristics                  | 46   |

| 2.3  | GATE DIELECTRIC ENGINEERING                          | 49   |

| 2.4  | CHANNEL ENGINEERING                                  | 53   |

| 2.5  | DEVICE ENGINEERING                                   | 56   |

|      | 2.5.1 Silicon on Insulator (SOI) MOSFET              | 57   |

|      | 2.5.2 Junctionless Field Effect Transistor           | 58   |

| 2.6  | TECHNICAL GAPS AS OBSERVED IN THE LITERATUR          | E 61 |

| 2.7  | CONCLUSION                                           | 61   |

| CHA  | <b>APTER –III ANALYSIS OF DOUBLE GATE SOI MOSFET</b> |      |

| 3.1  | INTRODUCTION                                         | 63   |

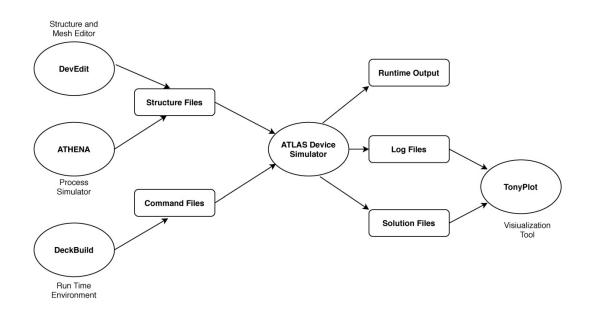

| 3.2  | TECHNOLOGY COMPUTER-AIDED DESIGN (TCAD)              | 64   |

|      | 3.2.1 Process Simulators                             | 64   |

|      | 3.2.2 Device Simulators                              | 65   |

| 3.3  | METHODOLOGY USED FOR SCALING                         | 66   |

| 3.4  | EFFECTS OF SCALING ON MOSFET                         | 66   |

|      | 3.4.1 Device Parameters Under Analysis               | 66   |

| 3.5  | NUMERICAL SIMULATIONS OF BULK MOSFET                 | 66   |

|      | STRUCTURES                                           |      |

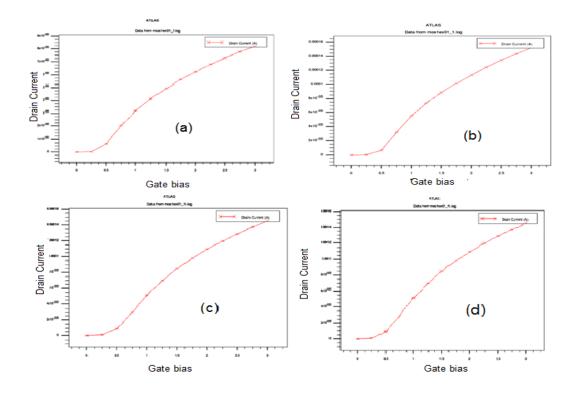

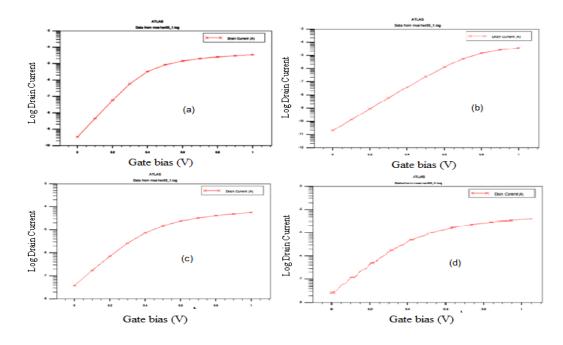

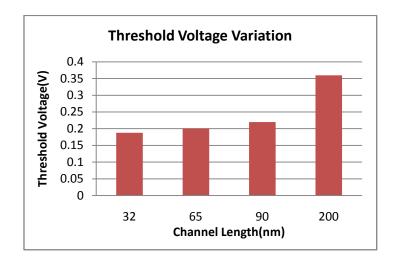

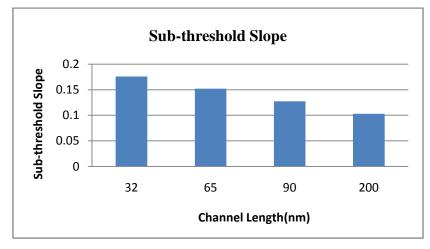

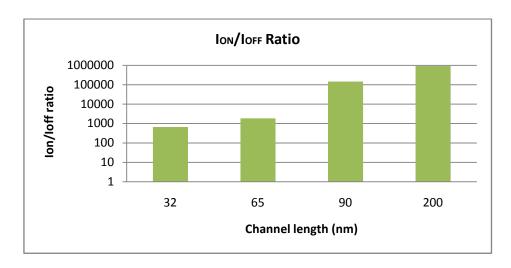

|      | 3.5.1 Planar NMOSFET Design at Different Node        | 67   |

|      | 3.5.2 Variation in Different Parameters with Scaling | 69   |

| 3.6  | CONCLUSION FROM SCALING                              | 71   |

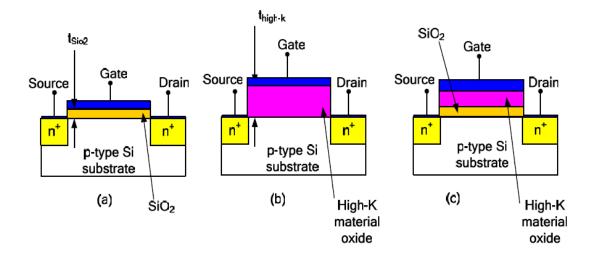

| 3.7  | LIMITATIONS WITH DEVICE MINIATURIZATION AND          | 71   |

| 3.8   | HIGH_  | -k GATE MATERIALS                                                                     | 72 |  |

|-------|--------|---------------------------------------------------------------------------------------|----|--|

| 3.9   |        |                                                                                       | 74 |  |

| 5.7   | 3.9.1  |                                                                                       |    |  |

|       | 5.7.1  | Material                                                                              | 75 |  |

| 3.9.2 |        | NMOSFET at 32 nanometer with Multioxide (SiO <sub>2</sub>                             | 76 |  |

|       |        | +HfO <sub>2</sub> ) as Dielectric Gate Material                                       |    |  |

|       | 3.9.3  | NMOSFET at 32 nanometer with High-k (HfO <sub>2</sub> ) as                            | 77 |  |

|       |        | Dielectric Gate Material                                                              |    |  |

|       | 3.9.4  | Comparisons of 32 nm NMOSFET Characteristics with                                     | 78 |  |

|       |        | Different Oxide Material                                                              |    |  |

|       | 3.9.5  | Effect of High – k Material on Various Parameters                                     | 79 |  |

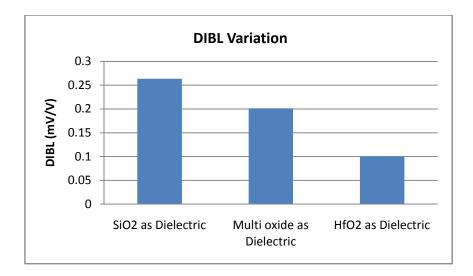

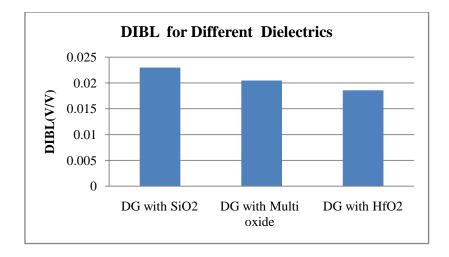

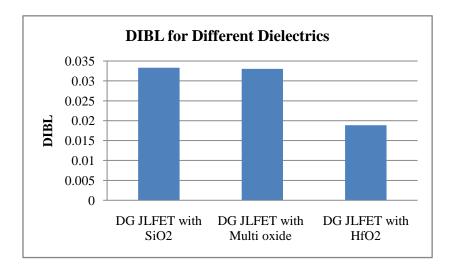

|       |        | 3.9.5.1 Effect of high –k material on DIBL                                            | 79 |  |

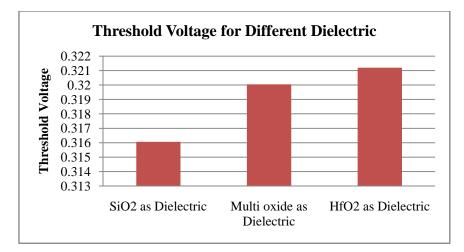

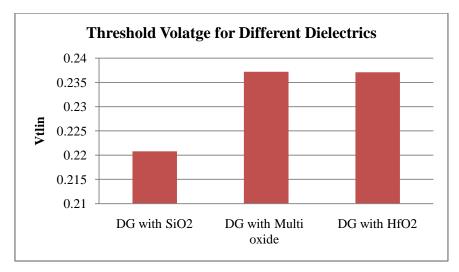

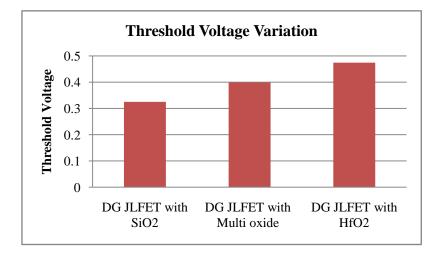

|       |        | 3.9.5.2 Effect of high –k material on threshold voltage                               | 80 |  |

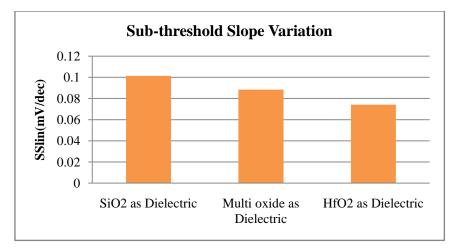

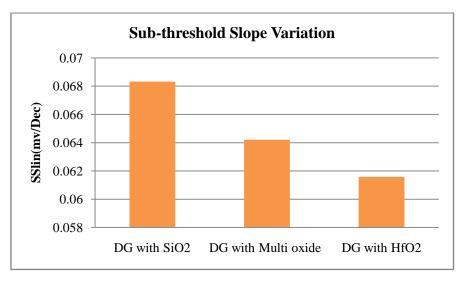

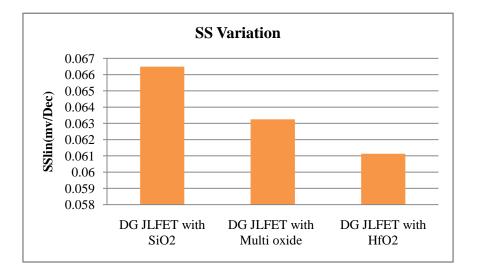

|       |        | 3.9.5.3 Effect of high –k material on sub-threshold slope                             | 81 |  |

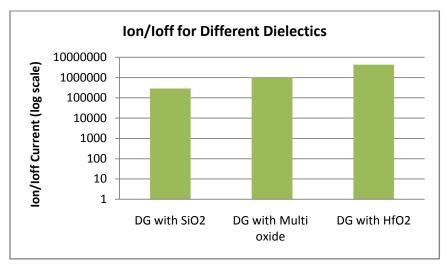

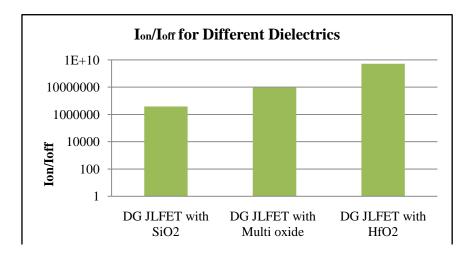

|       |        | 3.9.5.4 Effect of high –k material on I <sub>on</sub> /I <sub>off</sub> current ratio | 82 |  |

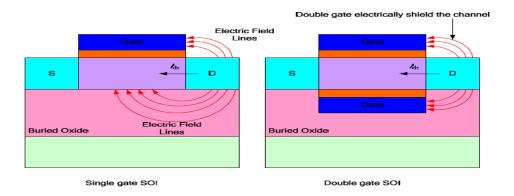

| 3.10  | MULT   | IPLE GATE MOSFET                                                                      | 83 |  |

| 3.11  | DOUB   | LE GATE MOSFET                                                                        | 83 |  |

|       | 3.11.1 | Advantage of Double Gate MOSFET                                                       | 84 |  |

|       | 3.11.2 |                                                                                       | 84 |  |

| 3.12  | SOI MO | OSFET                                                                                 | 85 |  |

|       | 3.12.1 | Advantages of SOI MOSFET                                                              | 85 |  |

|       | 3.12.2 | •                                                                                     | 86 |  |

| 3.13  | DOUB   | LE GATE SOI (DG-SOI) STRUCTURE                                                        | 87 |  |

| 3.14  | PERFC  | DRMANCE IMPROVEMENTS IN DG-SOI MOSFETS                                                | 88 |  |

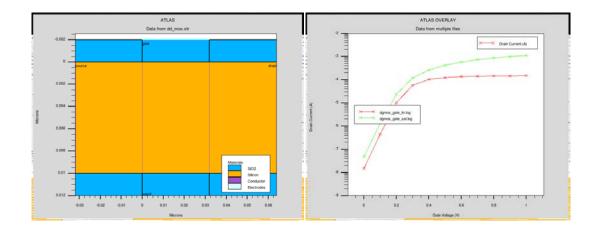

|       | 3.14.1 | DG-SOI NMOSFET at 32 nanometres with SiO <sub>2</sub> as                              | 89 |  |

|       |        | Dielectric Gate Material                                                              |    |  |

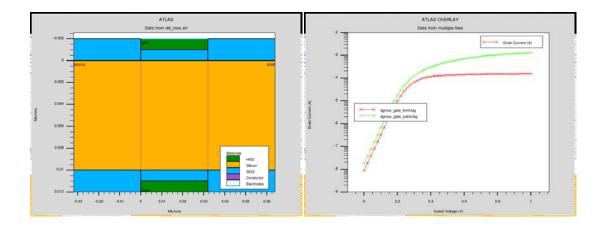

|       | 3.14.2 | DG-SOI NMOSFET at 32 nanometres with Multi oxide                                      | 89 |  |

|       |        | (SiO <sub>2</sub> +HfO <sub>2</sub> ) as Dielectric Gate Material                     |    |  |

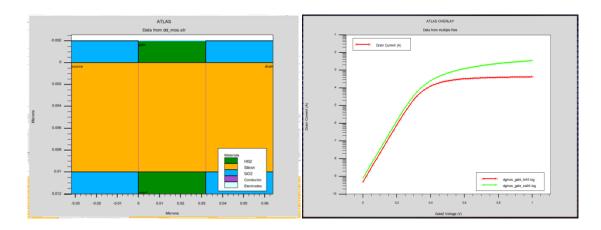

|       | 3.14.3 | DG-SOI NMOSFET at 32 nanometres with HfO <sub>2</sub> as                              | 90 |  |

|       |        | Dielectric Gate Material                                                              |    |  |

|       | 3.14.4 | Comparisons of 32 nm N-type DG MOSFET                                                 | 91 |  |

|       |        | Characteristics with Different Oxide Material                                         |    |  |

|       | 3.14.5 | Effect of High-k Material on Various Parameters for N-                                | 92 |  |

|       |        | type DG-SOI MOSFET                                                                    |    |  |

|       |        | 3.14.5.1 Effect of high-k material on DIBL in N-type                                  | 92 |  |

|       |        | DG-SOI MOSFET                                                                         |    |  |

|       |        | 3.14.5.2 Effect of high-k material on threshold voltage                               | 93 |  |

|       |        | in N-type DG-SOI MOSFET                                                               |    |  |

|       |        | 3.14.5.3 Effect of high-k material on the sub-threshold                               | 94 |  |

|       |        | slope in N-type DG-SOI MOSFET                                                         |    |  |

|       |        | 3.14.5.4 Effect of high-k material on I <sub>ON</sub> /I <sub>OFF</sub> current       | 94 |  |

|       |        | ratio in N-type DG-SOI MOSFET                                                         |    |  |

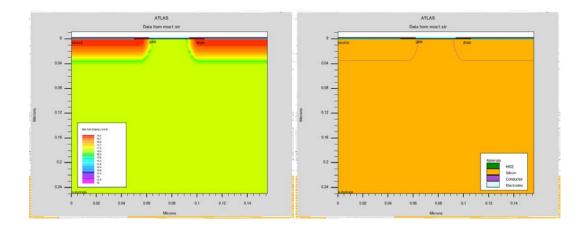

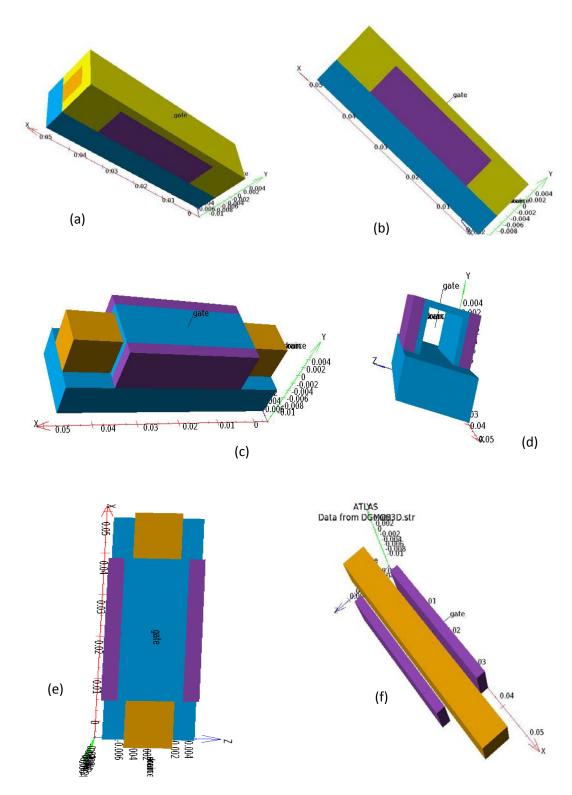

| 3.15  | THREE  | E DIMENSIONAL (3D) VIEW OF 32 NM N-TYPE DG                                            | 95 |  |

|       | MOSFET |                                                                                       |    |  |

# CHAPTER –IV ANALYTICAL MODELLING AND SIMULATION OF JUNCTIONLESS TRANSISTOR

4.1 INTRODUCTION

97

| 4.2  | JUNC   | TIONLES             | S FIELD EFFECT TRANSISTORS (JLFET)                            | 97         |

|------|--------|---------------------|---------------------------------------------------------------|------------|

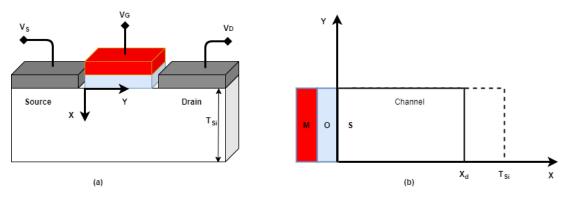

| 4.3  | DEVI   | CE STRU             | CTURE AND OPERATION                                           | 98         |

| 4.4  | MOD    | DDELING OF FETS 1   |                                                               |            |

| 4.5  | VARI   | IOUS FET MODELING 1 |                                                               |            |

| 4.6  | ANAI   | LYTICAL             | MODEL FOR THRESHOLD VOLTAGE AND                               | 101        |

|      | SURF   | ACE POT             | ENTIAL OF JLFETs                                              |            |

|      | 4.6.1  | Parabo              | lic Approximation Technique for Modelling DG-                 | 105        |

|      |        | JLFET               |                                                               |            |

|      | 4.6.2  |                     | Channel JLFETs Modelling                                      | 107        |

|      |        |                     | Quasi-2D scaling equation                                     | 108        |

| 4.7  |        |                     | SIMULATION OF DOUBLE GATE                                     | 112        |

|      |        |                     | S OF FIELD EFFECT TRANSISTOR (DG-JLFET)                       |            |

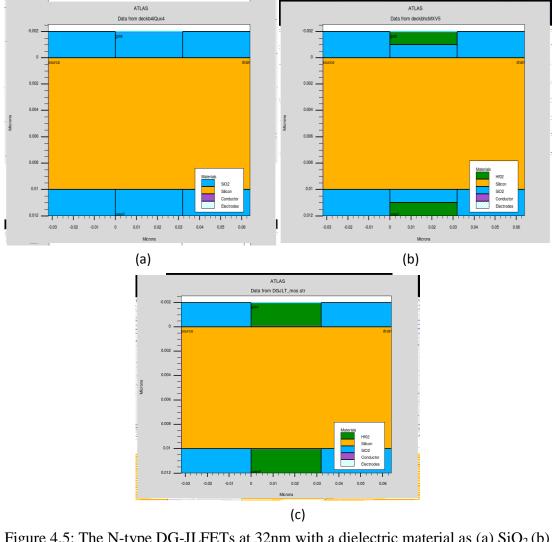

|      | 4.7.1  |                     | DG-JLFET at 32 nanometres with SiO <sub>2</sub> as Dielectric | 113        |

|      | 470    | Gate M              |                                                               | 115        |

|      | 4.7.2  |                     | of High-k Material on Various Parameters for N-type           | 115        |

|      |        | DG-JLI              |                                                               | 115        |

|      |        | 4.7.2.1             | Effect of high-k material on DIBL in N-type DG-<br>JLFETs     | 115        |

|      |        | 4.7.2.2             | Effect of high-k material on threshold voltage in             | 116        |

|      |        |                     | N-type DG-JLFETs                                              |            |

|      |        | 4.7.2.3             | Effect of high-k material on the sub-threshold                | 117        |

|      |        |                     | slope in N-type DG-JLFETs                                     |            |

|      |        | 4.7.2.4             | 8                                                             | 117        |

|      |        |                     | in N-type DG-JLFETs                                           |            |

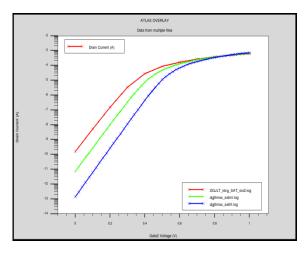

| 4.8  |        |                     | E RESULTS ACROSS VARIOUS STRUCTURES                           | 118        |

|      |        |                     | E OXIDES                                                      |            |

| 4.9  |        |                     | DISCUSSION                                                    | 121        |

|      | 4.9.1  | Surface I           |                                                               | 121        |

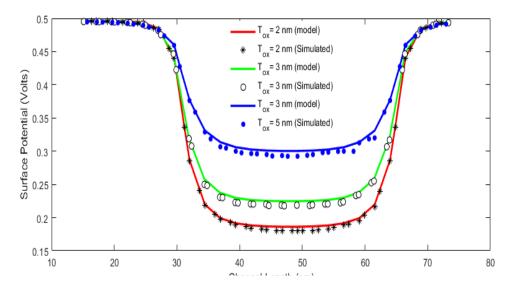

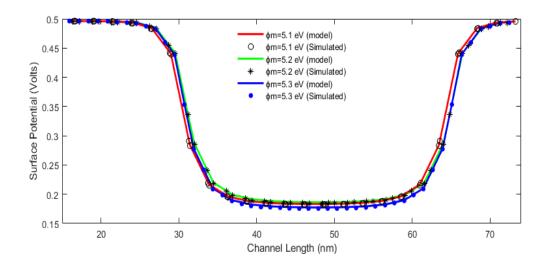

|      |        | 4.9.1.1             |                                                               | 121        |

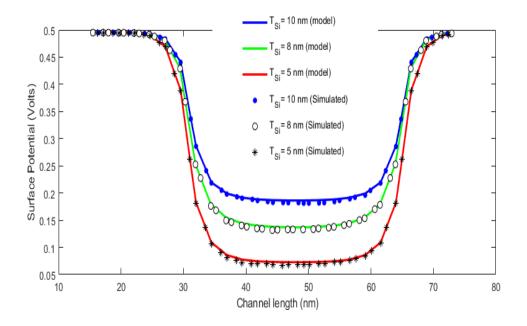

|      |        |                     | Silicon channel thickness variation                           | 122        |

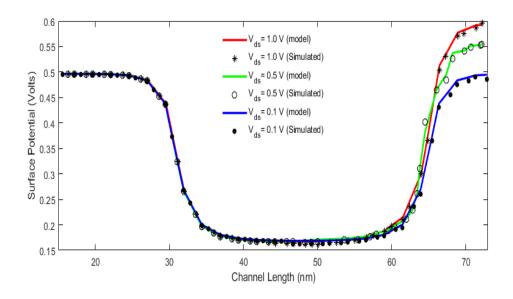

|      |        |                     | Variation of drain to source bias                             | 123        |

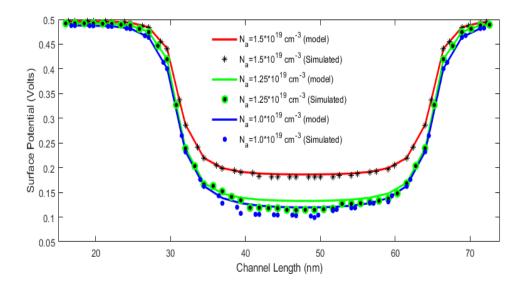

|      |        | 4.9.1.4             | Variation in Channel doping                                   | 123        |

|      | 402    |                     | Variation in gate work-function                               | 124        |

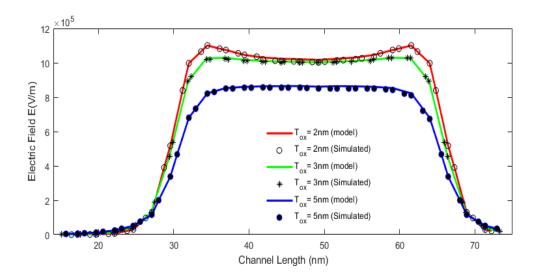

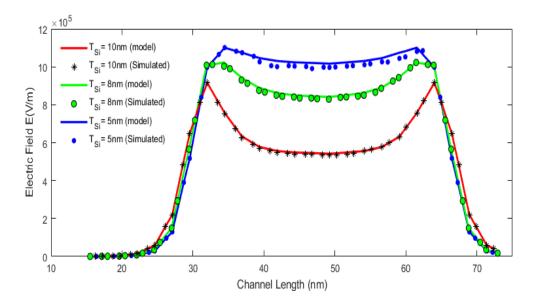

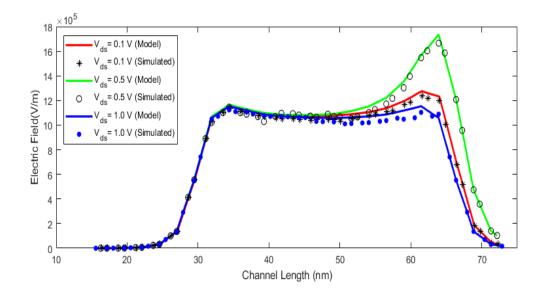

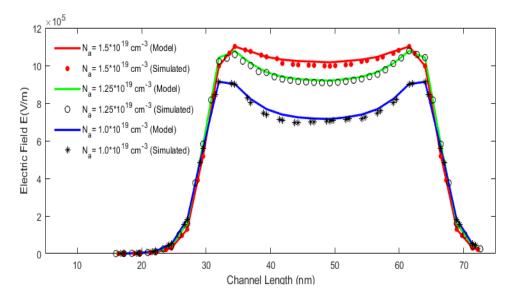

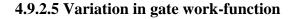

|      | 4.9.2  |                     | Field Distribution                                            | 125        |

|      |        | 4.9.2.1             | Oxide thickness variation                                     | 125        |

|      |        | 4.9.2.2<br>4.9.2.3  |                                                               | 126<br>126 |

|      |        | 4.9.2.3             |                                                               | 120        |

|      |        | 4.9.2.4             | Variation in gate work-function                               | 127        |

| 4.10 | CONC   | CLUSION             | variation in gate work-runction                               | 120        |

| 7.10 | CONC   |                     |                                                               | 127        |

| CHAI | PTER-V |                     | LYTICAL MODELING OF SUB-THRES                                 |            |

|      |        |                     | ENT FOR SD-TM-CGAA-JLFET DEVICE FOR<br>R CMOS INVERTER        | LUW        |

|      |        | LOWEI               |                                                               |            |

| 5.1 | INTRODUCTION                                     | 131 |

|-----|--------------------------------------------------|-----|

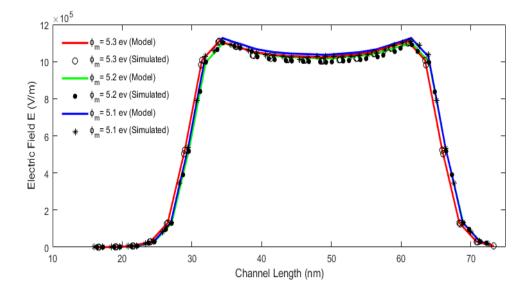

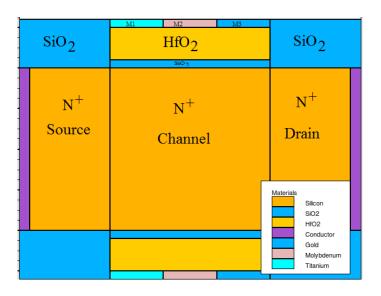

| 5.2 | DEVICE STRUCTURE                                 | 133 |

| 5.3 | ANALYTICAL MODEL OF SD-TM-CGAA-JLFET             | 134 |

|     | 5.3.1 Analytical Model for Sub-threshold Current | 135 |

|     | 5.3.2 Sub-threshold Slope                        | 137 |

| 5.4 | NUMERICAL SIMULATION OF SD-TM-CGAA-JLFET         | 138 |

| 5.5   | RESULTS AND DISCUSSION 139 |            |                                |     |

|-------|----------------------------|------------|--------------------------------|-----|

|       | 5.5.1                      | Sub-thre   | shold Current                  | 139 |

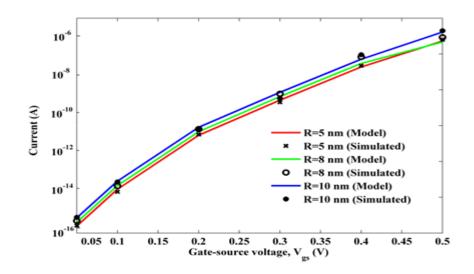

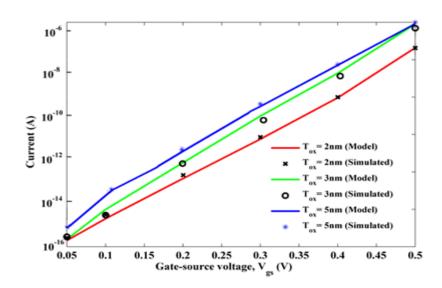

|       |                            | 5.5.1.1    | Silicon thickness variation    | 139 |

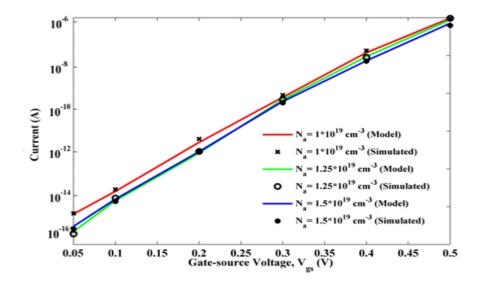

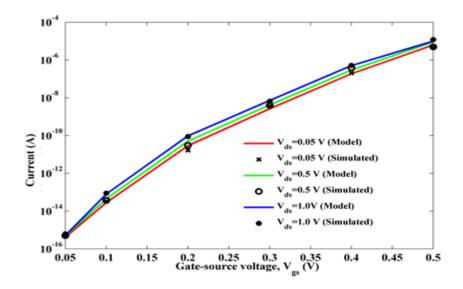

|       |                            | 5.5.1.2    | Channel doping variation       | 140 |

|       |                            | 5.5.1.3    | Oxide thickness variation      | 140 |

|       |                            | 5.5.1.4    | Drain to source bias variation | 141 |

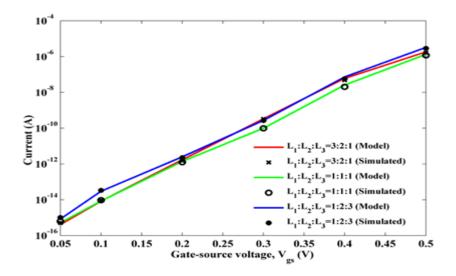

|       |                            | 5.5.1.5    | Channel length ratio variation | 141 |

|       | 5.5.2                      | Sub-thre   | shold Slope (SS)               | 142 |

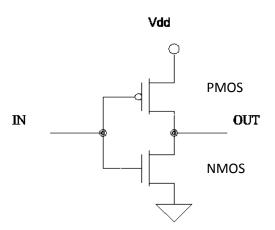

| 5.6   | INVE                       | RTER CIF   | RCUIT IMPLEMENTATION           | 142 |

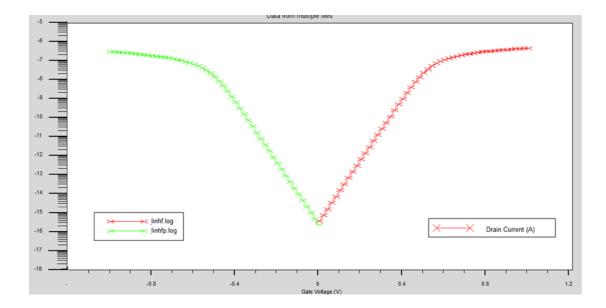

| 5.7   | SD-TI                      | M-CGAA-    | JLFET BASED PMOS               | 143 |

| 5.8   | CMO                        | S INVERT   | TER CHARACTERISTICS            | 144 |

| 5.9   | POWI                       | ER DISSIF  | PATION OF CMOS INVERTER        | 146 |

| 5.10  | CONC                       | CLUSION    |                                | 146 |

| CHA   | PTER –                     | VI CON     | CLUSION AND FUTURE SCOPE       |     |

| 6.1   | CONO                       | CLUSION    |                                | 149 |

| 6.2   | FUTU                       | RE SCOP    | PE                             | 151 |

| REFE  | ERENC                      | ES         |                                | 153 |

| Brief | profile                    | of the Car | ndidate                        | 175 |

|       | f Public                   |            |                                | 177 |

# LIST OF TABLES

- **Table 1.1**Various Types of Scaling

- Table 3.1

Extracted Parameters of NMOSFET for Different Technology Node

- **Table 3.2**32nm Bulk NMOS Characteristics with SiO2, Multi oxide and HfO2

- Table 3.3

32nm N-type DG-SOI MOSFET Characteristics with Different Oxide

- Table 4.1

32nm N-type DG-JLFETs Characteristics with Different Oxide

- Table 5.1

List of Constants and their Values for NMOS

# **LIST OF FIGURES**

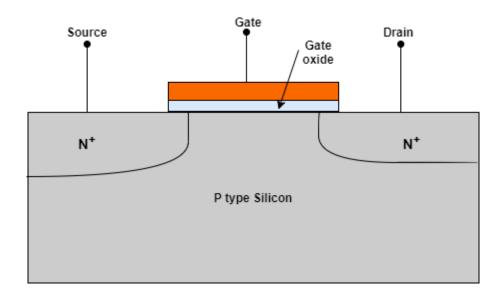

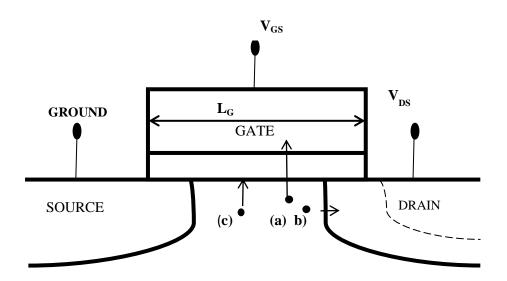

- Figure 1.1 Basic construction of n-channel MOSFET

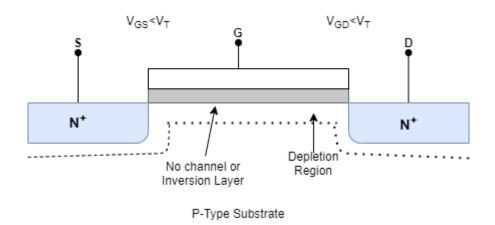

- Figure 1.2 MOSFET cutoff mode operation

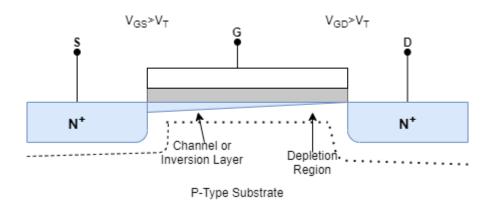

- Figure 1.3 MOSFET linear mode operation

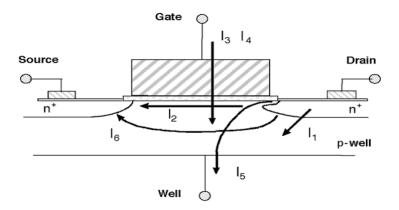

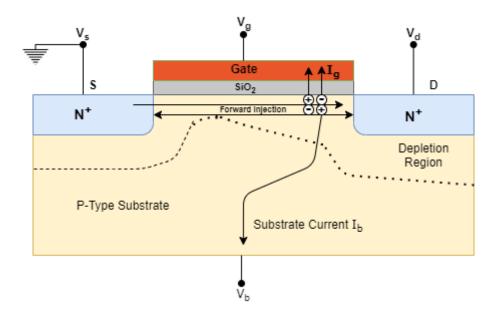

- Figure 1.4 MOS device leakage currents

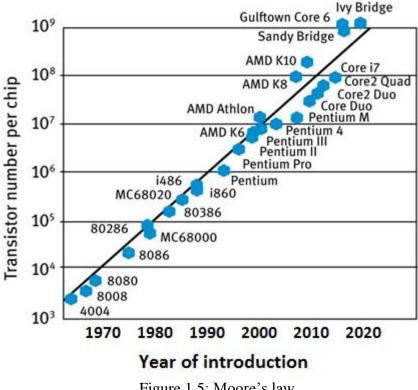

- Figure 1.5 Moore's law

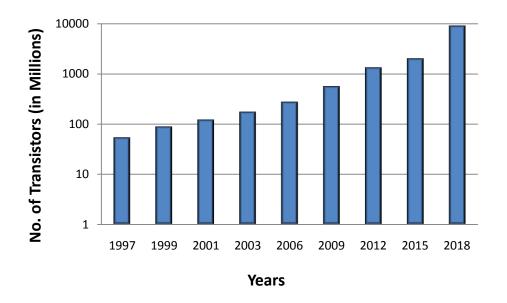

- **Figure 1.6** The increasing number of transistors per chip with device technology

- Figure 1.7 Impact Ionization

- Figure 1.8 Channel Length Modulation

- Figure 1.9 Hot carrier effects in MOSFETs

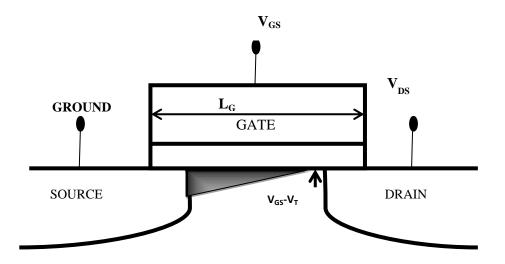

- Figure 1.10 MOSFET cross-sectional view indicating fringing lines

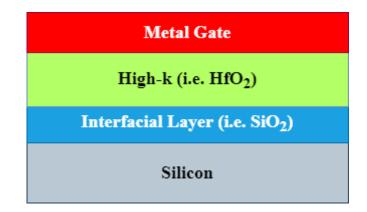

- Figure 1.11 Gate stack architecture

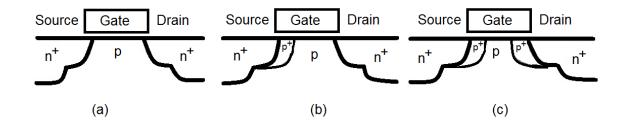

- **Figure 1.12** (a) Conventional MOSFET, (b) Asymmetric halo doping, (c) Symmetric halo doping

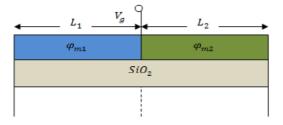

- Figure 1.13 Multi-material gate structure

- Figure 1.14 (a) PD SOI, (b) FD SOI transistor

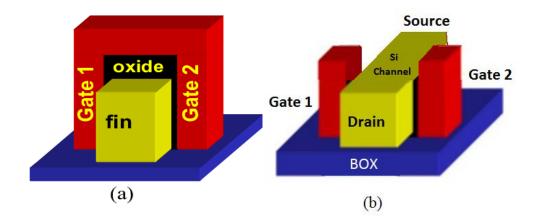

- **Figure 1.15** (a) Symmetric Double Gate MOSFET (b) Asymmetric Double Gate MOSFET

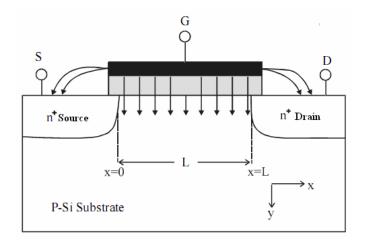

- Figure 1.16 Structure of Junction-Less Field-Effect Transistor

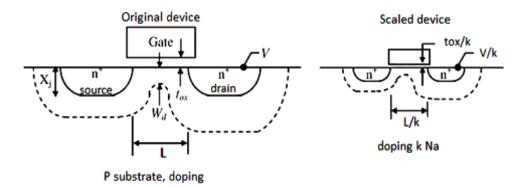

- Figure 3.1 Scaling of MOSFET

- Figure 3.2 Flow of data in SILVACO TCAD TOOL

- Figure 3.3 Simulated structures of NMOS at (a) 200nm (b) 90nm (c) 65nm and (d) 32nm

- **Figure 3.4** Transfer Characteristic of NMOS at(a) 200nm (b) 90nm (c) 65nm and (d) 32nm channel length

- **Figure 3.5** NMOSFET transfer characteristics plots for (a) 200nm (b) 90nm (c) 65nm and (d) 32nm channel length

- Figure 3.6 Threshold voltage variation with channel length

- Figure 3.7 Sub-threshold slope variation for channel length

- Figure 3.8 I<sub>ON</sub>/I<sub>OFF</sub> variation with different channel length

- **Figure 3.9** Cross-sectional structure of bulk NMOS having gate dielectric as (a)  $SiO_2$  (b) High-k (c) Gate stack of High-k +SiO<sub>2</sub>.

- Figure 3.10 32nm Bulk N-MOSFET a) Material view and b) Doping density view

- Figure 3.11 Transfer characteristics for bulk MOSFET with SiO<sub>2</sub> as the dielectric

- **Figure 3.12** 32nm Bulk N-MOSFET a) Material view and b) doping density view using multi oxide (SiO<sub>2</sub>+HfO<sub>2</sub>)

- Figure 3.13 32nm Bulk N-MOSFET with multi oxide stack architecture

- **Figure 3.14** Transfer characteristics for bulk MOSFET with multi oxide as the dielectric

- **Figure 3.15** 32nm Bulk N-MOSFET a) Material view and b) Doping density view using high-k (HfO<sub>2</sub>).

- Figure 3.16 Transfer characteristics for bulk MOSFET with high-k as a dielectric

- Figure 3.17 32nm NMOS transfer characteristics with SiO<sub>2</sub>, Multi oxide and HfO<sub>2</sub>

- Figure 3.18 DIBL for 32nm bulk MOSFET with different dielectric materials

- Figure 3.19 Threshold voltage variation on the application of high-k dielectric

- Figure 3.20 Variation of the sub-threshold slope with different dielectrics.

- Figure 3.21 Variation of I<sub>ON</sub>/I<sub>OFF</sub> with different dielectric materials

- **Figure 3.22** Drain field lines impact on SOI structure with (a) Single gate (b) Double gate

- Figure 3.23 DG-SOI MOSFET with (a) Inactive top gate (b) Two gates

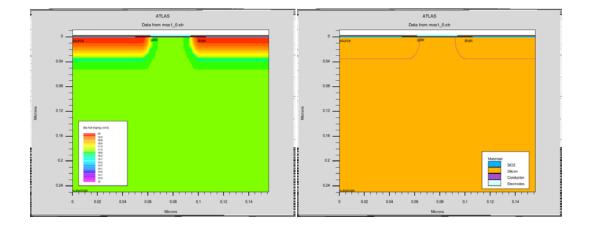

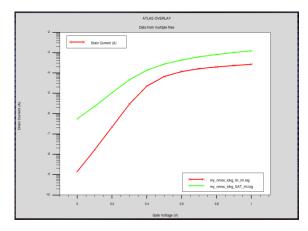

- **Figure 3.24** 32nm N-type DG-SOI MOSFET having SiO<sub>2</sub> dielectric a) Material view (b) Transfer characteristics

- **Figure 3.25** 32nm N-type DG-SOI MOSFET having Multi oxide (SiO<sub>2</sub>+HfO<sub>2</sub>) dielectric a) Material view (b) Transfer characteristics

- **Figure 3.26** 32nm N-type DG-SOI MOSFET having HfO<sub>2</sub> dielectric a) Material view (b) Transfer characteristics

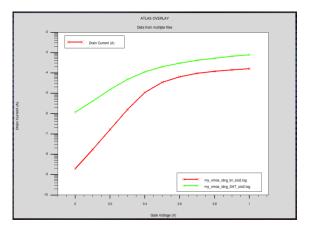

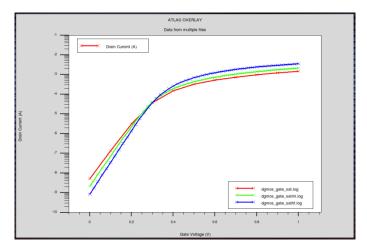

- **Figure 3.27** 32nm N-type DG-SOI MOSFET transfer characteristics with SiO<sub>2</sub>, multi oxide and HfO<sub>2</sub>

- Figure 3.28 DIBL for 32nm N-type DG-SOI MOSFET with different dielectric materials

- Figure 3.29 Threshold voltage variation with different dielectrics.

- Figure 3.30 Sub-threshold slope variation with different dielectrics

- Figure 3.31 Variation of I<sub>ON</sub>/I<sub>OFF</sub> with different dielectric materials

- Figure 3.32 3D architecture of DG-SOI MOSFET with various abstract layers (a) 3D view (b) 3D view from gate side (c) 3D view with vacuum removed (d) 3D view with vacuum and silicon removed (e) 3D top view with vacuum removed with double gate (f) 3D view with gate and silicon material (oxide layer removed)

- Figure 4.1 Structure of Junctionless Field-Effect Transistor

- Figure 4.2 (a) Single-Gate JLFET (b) Silicon Depletion Charge Profile

- Figure 4.3 Double Gate JLFET.

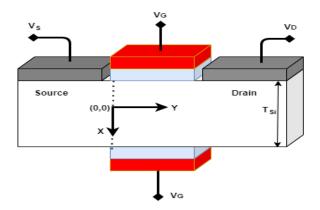

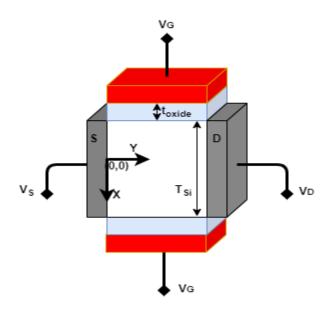

- Figure 4.4 Short-channel DG-JLFET.

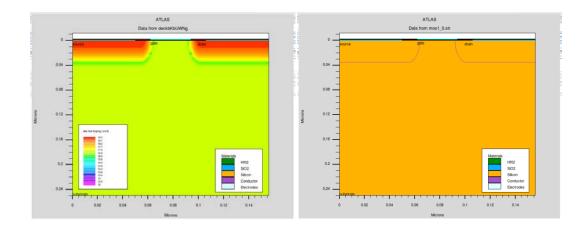

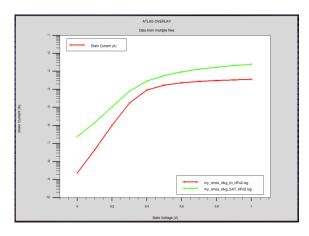

- **Figure 4.5** The N-type DG-JLFETs at 32nm with dielectric material as (a) SiO<sub>2</sub> (b) Multi oxide (SiO<sub>2</sub>+HfO<sub>2</sub>) and (c) HfO<sub>2</sub>

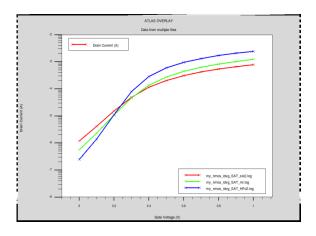

- **Figure 4.6** 32nm N-type DG-JLFETs transfer characteristics with SiO<sub>2</sub>, Multi oxide and HfO<sub>2</sub> as gate dielectric materials.

- Figure 4.7 DIBL for 32nm N-type DG-JLFETs with different dielectric materials.

- Figure 4.8 Threshold voltage variation with different dielectrics

- Figure 4.9 Sub-threshold slope variation with different dielectrics.

- Figure 4.10 Variation of I<sub>ON</sub>/I<sub>OFF</sub> for DG-JLFETs with different dielectric materials

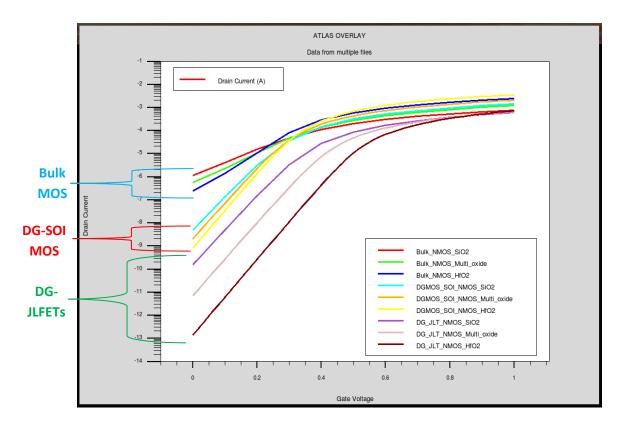

- Figure 4.11 Transfer characteristics for all the structures for various oxides

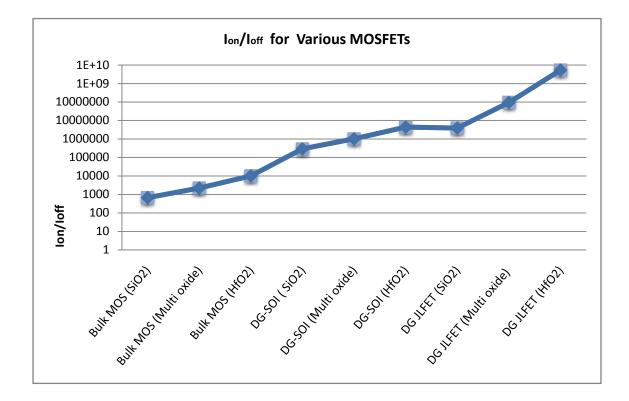

- Figure 4.12  $I_{ON}/I_{OFF}$  ratio for all the MOS structures

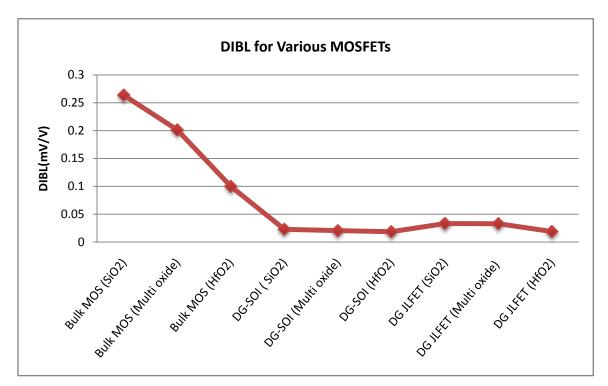

- Figure 4.13 DIBL for various MOSFETs structures

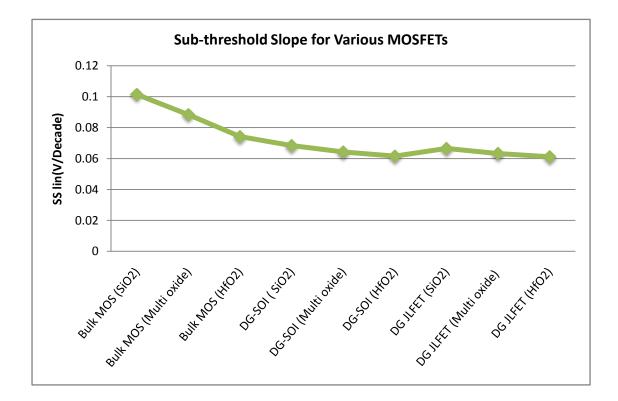

- Figure 4.14 Sub-threshold slope for various MOSFETs structures

| Figure 4.15 | Variation in surface potential profile along with channel length for                                                                     |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Figure 4.16 | various oxide thicknesses<br>Variation in surface potential profile along with channel length for<br>various silicon channel thicknesses |  |  |

| Figure 4.17 | Variation in surface potential profile along with channel length for<br>various drain to source bias                                     |  |  |

| Figure 4.18 | Variation in surface potential profile along with channel length for various channel doping                                              |  |  |

| Figure 4.19 | Variation in surface potential profile along with channel length for various gate work-function                                          |  |  |

| Figure 4.20 | Variation in the electric field along with channel length for various silicon oxide thickness                                            |  |  |

| Figure 4.21 | Variation in the electric field along with channel length for various silicon channel thickness variation                                |  |  |

| Figure 4.22 | Variation in the electric field along with channel length for various drain to source bias                                               |  |  |

| Figure 4.23 | Variation in the electric field along with channel length for various channel doping                                                     |  |  |

| Figure 4.24 | Variation in the electric field along with channel length for various gate work-function                                                 |  |  |

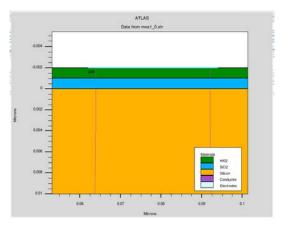

| Figure 5.1  | 3D View of SD-TM-CGAA-JLFET                                                                                                              |  |  |

| Figure 5.2  | Cross-sectional view of SD-TM-CGAA-JLFET                                                                                                 |  |  |

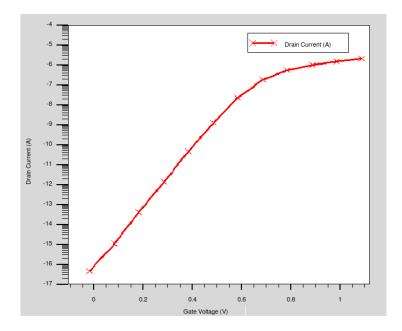

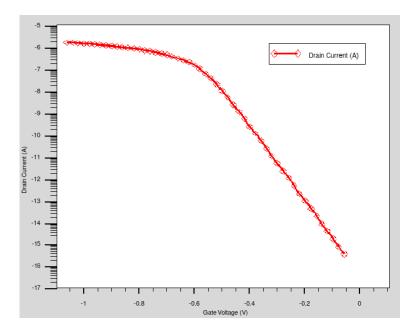

| Figure 5.3  | Transfer characteristics of SD-TM-CGAA-JLFET                                                                                             |  |  |

| Figure 5.4  | Variation in off current with $V_{gs}$ for various silicon channel thickness                                                             |  |  |

| Figure 5.5  | Variation in off current with $V_{gs}$ for various channel doping concentrations                                                         |  |  |

| Figure 5.6  | Variation in off current with $V_{gs}$ for various oxide thickness                                                                       |  |  |

| Figure 5.7  | Variation in off current with $V_{gs}$ for various drain bias                                                                            |  |  |

| Figure 5.8  | Variation in off current with $V_{gs}$ for various device length ratio.                                                                  |  |  |

| Figure 5.9  | CMOS Inverter                                                                                                                            |  |  |

| Figure 5.10 | Transfer characteristics of the P-type SD-TM-CGAA-JLFET device                                                                           |  |  |

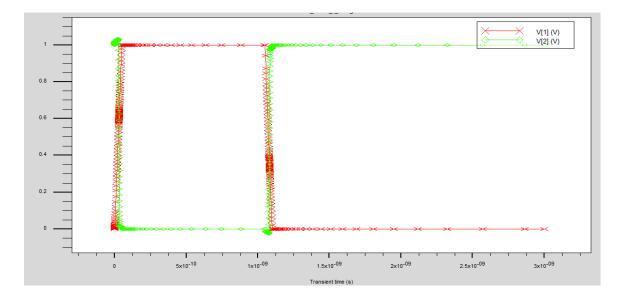

| Figure 5.11 | Transient characteristics of CMOS Inverter                                                                                               |  |  |

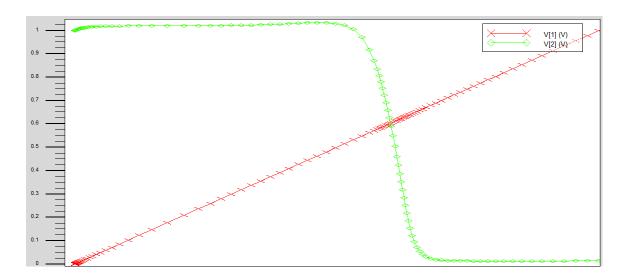

| Figure 5.12 | DC characteristics of CMOS Inverter                                                                                                      |  |  |

| Figure 5.13 | The V-curve of CMOS Inverter                                                                                                             |  |  |

|             |                                                                                                                                          |  |  |

# LIST OF SYMBOLS

| μ                      | Mobility                                |

|------------------------|-----------------------------------------|

| $C_{\text{oxide}}$     | Oxide capacitance                       |

| Е                      | Electric Field                          |

| Eg                     | Energy Band gap                         |

| g <sub>m</sub>         | Transconductance                        |

| $g_m/I_d$              | Transconductance to Drain Current Ratio |

| I <sub>sub</sub>       | Sub-threshold Current                   |

| I <sub>ds</sub>        | Drain to Source Current                 |

| J <sub>C</sub> (r,z)   | Total Current Density                   |

| Κ                      | Boltzmann Constant                      |

| L                      | Channel Length                          |

| $M_1, M_2, M_3$        | Gate Materials                          |

| N <sub>a</sub>         | Acceptor Concentration                  |

| N <sub>C</sub> (r,z)   | Carrier Concentration                   |

| $N_d$                  | Donor Concentration                     |

| n <sub>i</sub>         | Intrinsic Carrier Concentration         |

| $\phi_{\mathrm{fp}}$   | Fermi Potential                         |

| $\Psi_{S}$             | Surface Potential                       |

| $\Psi_{\text{OXIDE}}$  | Potential drop across the gate oxide    |

| $\Psi_0$               | Center Potential                        |

| $\phi_{\mathrm{M1}}$   | Work Function for Metal 1               |

| $\phi_{M2}$            | Work Function for Metal 2               |

| <b>ф</b> <sub>M3</sub> | Work Function for Metal 3               |

| $\Psi_{\text{min}}$    | Minimum Surface Potential               |

| q                      | Electronic Charge                       |

| Т                      | Temperature                             |

| $t_{\rm HfO2}$         | Thickness of Hafnium Oxide              |

| $t_{\rm SiO2}$         | Thickness of Silicon Oxide              |

| t <sub>oxide</sub>     | Thickness of Oxide Layer                |

| t <sub>si</sub>        | Silicon Film thickness                  |

| $V_{bi}$               | Built in Potential                      |

| V <sub>ds</sub>        | Drain-Source Voltage                    |

| $V_{\mathrm{f}}$       | Flat-band Voltage                       |

| $\mathbf{V}_{\mathrm{gs}}$ | Gate-Source Voltage                       |

|----------------------------|-------------------------------------------|

| $V_{th}$                   | Threshold Voltage                         |

| $\epsilon_{\rm SiO2}$      | Permittivity of Silicon Oxide             |

| $L_1$                      | Channel Length under metal M <sub>1</sub> |

| $L_2$                      | Channel Length under metal M <sub>2</sub> |

| $L_3$                      | Channel Length under metal M <sub>3</sub> |

| $V_{th}$                   | Threshold Voltage                         |

| $V_{DD}$                   | Positive Supply Voltage                   |

| Pdynamic                   | Dynamic Power Dissipation                 |

| fck                        | Clock Frequency                           |

| PSC                        | Short Circuit Power Dissipation           |

| k                          | Dielectric Constant                       |

| 2D                         | Two Dimensional                           |

| Ion                        | On-current                                |

| $I_{off}$                  | Off-current                               |

| Vt <sub>sat</sub>          | Saturation Threshold Voltage              |

| $Vt_{lin}$                 | Linear Threshold Voltage                  |

| SS                         | Sub-threshold Slope                       |

# **CHAPTER-I**

# **INTRODUCTION**

## **1.1 PREAMBLE**

The discovery of the transistor and subsequently the monolithic integrated circuit (IC) has created a revolution in the field of the electronics industry. Semiconductor technology has grown at a very fast pace in the last 70 years. The first semiconductor transistor was invented in 1947 at Bell Laboratory by W. Shockley, J. Bardeen and W. Brattain [1]. It completely replaced the vacuums tubes from the entire electronics product. After the invention of the transistor, there is no looking back for the semiconductor electronics industry. The circuits where semiconductors devices are applied range from a very simple system to a very complex system having constraints of power, area, etc. The electronics industries have come up in the past to design and create semiconductor device-based circuits as small as basic gates and as complex as processors. The advancement in the fabrication technology with every generation of semiconductor devices, are producing smaller, faster as well as low-power integrated chips. This ultra-small design of integrated circuits requires advanced fabrication technology and capable fabrication equipment. With the advancements in computer technology for automated tools, a better understanding of electronics system design and applications software along with this improved process technology makes it possible to integrate billions of transistors on a single semiconductor wafer with device dimensions below 10 nanometres recently [2].

Moore's law states that the transistors in integrated circuits will get doubled every 18 months [3]. Continuous reduction in feature size has established the increase in device density on IC as per Moore's law for almost half-decade. The density improvement not only results in a reduction in the system design area but also improves processing speed and memory capacity in an exponential manner [3]. However, in deep submicron technologies, it enhances the sub-threshold current which causes more power consumption and subsequently reduced battery life. The continuous process of downscaling the semiconductor device dimensions is the main stimulant for the growth of integrated circuits and advancement in allied technology like robotics,

information communication technology, biotechnology, sensors, etc with superior performance and small size at a much-reduced cost.

The bipolar technology which was introduced in 1947 [4] was initially used for integrated circuits. Due to high power dissipation and limited level of integration over an IC, causes the semiconductor industry has to look for alternate semiconductor devices. Metal Oxide Field Effect Transistor (MOSFET) was initially conceptualized in the 1930s, but the first working MOSFET device was created in the 1960s [4]. The unique properties of MOSFETs make them a significant partner in the evolutionary progress of the semiconductor industry. The field of microelectronics today is dominated by MOSFET. The MOSFET or MOS transistor is the most commonly used semiconductor electronic device in the present era. In 1963 [4], with the advent of low power design technique, CMOS (Complementary MOS) where both NMOS and PMOS were fabricated on the same semiconductor substrate, the era of semiconductor technology changed forever. CMOS devices have better features, viz. high noise immunity, negligible standby power dissipation, significantly higher packing density, relatively faster circuit speed, lower energy wastage compared to NMOS and TTL (Transistor-Transistor Logic) [5].

As the number of semiconductor devices on integrated circuits increases, the size of each transistor and power supply is decreased or scaled. This scaling results in a decrease in power consumption, higher current drive and faster circuits leading to improved performance [5]. However, the scaling of MOSFET dimensions not only reduces the separation between the drain and source electrode but also decreases the control of the gate electrode. This reduction of the control of the gate electrode results in some undesirable effects called Short Channel Effects (SCEs). These effects include an adjustment in threshold voltage ( $V_{th}$ ), reduced subthreshold swing, lowering of the potential barrier and increased leakage current [6]. These effects also cause large power dissipation and reduction in the device performance.

With the steady improvement in device fabrication technology, MOSFET in the recent past has reached its scaling limit. The requirements to further scale these MOSFETs have introduced several inventive techniques composing of the use of new channel materials, new device structures and new gate oxide materials. The proposed materials by various researchers [4-6], devices and technology include the usage of

High-k materials, Silicon over Insulator (SOI), Dual/double/multi-gate device structures, Gate all-around devices (GAA) and recently Junctionless MOSFETs [7] among many others. The Junctionless MOSFETs promised to have better-scaling properties as compared to the multiple-gate MOSFETs.

#### **1.2. MOSFETS**

Advanced integrated circuits with reduced feature sizes are created every coming year. These semiconductor devices are not only cost-effective but also more reliable than their predecessor. The semiconductor industrial advancement in the past mainly depends on the success of integrated circuits made up of silicon-based devices known as Metal Oxide Semiconductor Field Effect Transistor (MOSFET). This semiconductor device is utilized as a switch as well as an amplifier.

MOSFET is a four-terminal device. A large number of MOSFETs and their interconnection can be created on the surface of the single integrated circuit due to the planner nature of this device. The integration of MOSFETs in Integrated Circuits (ICs) have been implemented through many generations of integration like MSI (Medium Scale Integration) includes 100-1000 transistors on an IC, LSI (Large Scale Integration) having 10<sup>3</sup>-10<sup>4</sup> transistors on an IC, VLSI (Very Large Scale Integration) having more than 10<sup>5</sup> transistors on an IC and ULSI (Ultra Large Scale Integration) where more than one million transistors are mounted on an IC [5].

MOSFET was designed with the idea of an insulated gate i.e. the gate leakage current should be minimum. MOSFET was created with the insulated gate so that no leakage current flows to or from the gate. In silicon MOSFETs, reliable and high-quality insulators can be grown easily in the form of Silicon Dioxide (SiO<sub>2</sub>). SiO<sub>2</sub> acts as an insulator that makes firm bonding with the silicon substrate. The SiO<sub>2</sub> not only works as an insulator in the MOSFET but also facilitates selective diffusion and pattern transfer during the fabrication of the device. Due to these benefits, silicon-based technology prevailed for MOSFET [8].

MOSFET is a unipolar device that controls the drain current by applying gate voltage. During MOSFET operation, the gate voltage is applied to create the channel that facilitates the charge carriers to flow from source to drain. Over the years many new concepts for semiconductor materials have been applied in MOSFETs for various applications but the high-quality oxide formation still makes the Silicon-based MOSFETs the preferred choice.

Enhancement type MOSFETs and Depletion type MOSFETs technology exist in MOSFETs. MOSFETs based on the charge carrier which participates in the charge conduction process are classified as N-channel MOSFET (nMOS) and P-channel MOSFET (pMOS). MOSFET consists of the drain, source, gate and substrate electrode. The source is normally connected to the substrate of MOSFET.

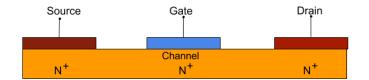

# **1.2.1** Construction of the MOSFET

Figure 1.1 depicts the construction of the enhancement type n-channel MOSFET. The substrate of the MOSFET is made with the lightly doped p-type semiconductor material. The two heavily n-doped regions are created to form source and drain regions having metallic contacts. Isolation between the gate electrode and channel (the region between source and drain) is created using Silicon dioxide (SiO<sub>2</sub>). The conductivity of the channel is modulated by gate bias.

The enhancement type and depletion type MOSFETs are the same from a construction point of view. However, a prefabricated channel exists in depletion type MOSFET.

Figure 1.1 Basic construction of n-channel MOSFET

The nMOS have charge carriers as electrons in the channel and the pMOS have charge carrier holes in the channel.

## **1.2.2 MOSFET Operation**

In MOSFET, when the appropriate voltage is applied at the gate terminal, a conducting channel is created which connects the drain and source using the minority charge carriers of the substrate.

In the absence of voltage on the gate terminal, the minority charge carriers are not able to accumulate under the gate region and the formation of the channel or the conducting path between the source and drain region does not take place which results in absence of drain current. When the positive voltage (in the case of nMOS), which is more than the threshold voltage is applied at the gate terminal, the electrons under the gate region start to accumulate under the gate region and a conducting channel gets created between the source and drain. The applied positive voltage on the gate terminal attracts the minority charge carriers (for substrate) i.e. electrons to form the n-type channel and also repels the majority charge carriers i.e. holes of the p-type substrate to deep inside the substrate.

When the appropriate voltage between source and drain is applied the drain current starts to flow in between the source and drain through this channel. When the voltage at the gate terminal is enhanced, more electrons get accumulated under the gate and holes move deeper inside the substrate, which results in the creation of a strong channel between source and drain. The strong channel is capable of conducting a large amount of drain current between drain and source. The device in which this process of gate voltage to create or to enhance the channel occurs is known as enhancement type MOSFET. The flow of the drain current can be controlled by the applied voltage at the gate terminal. Depending upon the applied voltage over the different terminals of MOSFET, the operation of MOSFET can be classified into three modes:

## 1.2.2.1 Cut-off mode

When the gate to source voltage ( $V_{gs}$ ) is below the threshold voltage ( $V_{th}$ ) (minimum voltage required for turning on the MOSFET), the MOS device is said to be operating in the cut-off region. Hence when  $V_{gs} < V_{th}$ , no current flows between the source and drain through the channel. The MOSFET in cut-off mode is shown in Figure 1.2

Figure 1.2: MOSFET cut-off mode operation [9].

## 1.2.2.2 Triode region or linear mode

When  $V_{gs} > V_{th}$ ,  $V_{gd} > V_{th}$ , with  $V_{ds} > 0$ , the MOS device is said to operate in triode or linear mode. In this mode, the voltage applied at the gate terminal is more than the threshold voltage, but the drain to source voltage is less than the difference of gate to source voltage and threshold voltage (drain gate to drain voltage is less than threshold voltage)

Figure 1.3: MOSFET linear mode operation [9].

This mode as shown in Figure 1.3 is also known as a linear or ohmic mode. In this mode, the drain current varies linearly with gate voltage and MOSFET behaves like a resistor in this mode.

#### 1.2.2.3 Saturation mode

When  $V_{gs} > V_{th}$ ,  $V_{gd} < V_{th}$  ( $V_{ds} > 0$ ), the MOS device is said to operate in saturation mode. In this mode, the gate to source voltage is higher in comparison to the threshold voltage and drain to source voltage is also greater than the gate to source and threshold voltage difference (or gate to drain is less than threshold voltage). The formation of a channel in saturation mode is maximum. Hence, a large current flows through the channel between the source and drain. In this mode, the drain current is almost constant and independent of drain voltage but only depends upon gate voltage.

The linear mode operation of the MOS device is useful for digital circuits and saturation mode is useful for analog circuits [9].

#### **1.2.3 Distinguished Features of MOSFET**

The distinguishing features of MOSFET with respect to other semiconductor devices are

- 1. Surface conduction.

- 2. Symmetrical doping in source and drain regions.

- 3. Channel barrier height controlled by the insulated gate.

- 4. Gate current is zero

5. Two physical mechanisms for current: Diffusion (in weak inversion mode / subthreshold conduction mode) and Drift (dominates in strong inversion)

6. Negligible second breakdown voltage [5].

### **1.3 ITRS ROADMAP FOR SEMICONDUCTORS**

International Technology Roadmap for semiconductors or ITRS [10] was conceptualized by various experts of the semiconductors field to specify the device design parameters for the future generation semiconductor devices. It also predicts the challenges that the device scaling industry might face with the future generation of devices. ITRS specifies the parameters by keeping high performance and power consumption issues in focus. Since the digital and memory-based IC production is a major portion of the semiconductor industries so the consideration for ITRS was always low power, high-speed performance and area requirements for the future generation of devices.

The approaches for attaining these targets are quite different i.e. the high-speed performance usually result in high off current or increased power consumption, low power approach maintain longer operating status of portable devices by the mean of reducing switching activities or the operating speed.

The ITRS ensures that research and development be continued in this area to maintain the historical scaling for future projections. ITRS is not updated from 2017 and International Roadmap for Devices and Systems (IRDS) [2] had replaced it to make predictions about the future development in the field of electronics systems and semiconductor devices.

### **1.4 TECHNOLOGY TRENDS IN POWER DISSIPATION**

In the recent past, most of the research in the semiconductors field is devoted to reducing the power dissipation of circuits. The omnipresent portable electronic devices have limited battery life but they require a longer operational lifetime. The semiconductor IC manufacturers are looking for new technologies and new circuit approaches to improve power performance without compromising on speed, area and reliability. In non-portables electronics systems too, the reduction of power consumption is an important concern due to the cost involved in cooling mechanism and system reliability. In order to obtain the high performance of the system, the low power operation is a major challenge in modern semiconductor integrated circuits. Many approaches like sub-threshold logic circuits where the semiconductor devices

are driven at the power supply voltage below threshold voltage are used. Here low power consumption is obtained at the cost of the performance of the circuit. In subthreshold circuits, the speed of operation reduces due to the increase in delay. The current is having an exponential dependency on gate voltage, temperature and threshold voltage in the sub-threshold region. However, the current has a linear dependence on the W/L (width to length of the device) ratio. Hence, the device size has much less effect on the device current than it would have been in the strong operating region [11]. The sub-threshold region's operation of the device results in an improvement in the characteristics like Voltage Transfer Characteristics (VTC) and noise margin.

It can be easily predicted that in the absence of low-powered operations, the portable devices either have a very short operation lifetime or require very heavy battery space. The cost of the system does increase in the absence of low power operations due to advanced packaging and cooling mechanism. The reliability issues are also faced in the non-low power systems as these systems dissipate power in terms of heat and this heat raises the temperature of the system. The high temperature tends to increase the possibility of silicon failure mechanism.

# **1.5 POWER DISSIPATION IN CMOS CIRCUITS**

CMOS circuits design approach composed of both pMOS and nMOS on the same silicon wafer which is generally a preferred low power choice for the systems. However, the major sources of power dissipation can be classified into three categories for CMOS circuits: Dynamic Power Dissipation, Short Circuit Power Dissipation and Static Leakage Power Dissipation.

In the initial stages of IC's era, dynamic power consumption was dominant and the remaining two power consumptions were almost negligible. The advent of short channel devices has caused the static leakages power to become the major component of power dissipation along with the other two mechanisms also playing a significant part [9]. A brief overview of different components of power dissipation in circuits is as under

## **1.5.1 Dynamic Power Dissipation**

When the transistor switches from one logic to another logic, the power is required for the charging and discharging of load capacitances. This power consumption is termed dynamic power dissipation. The dynamic power dissipation for a CMOS inverter may be understood by assuming a CMOS inverter having load capacitance as C and having supply voltage as  $V_{DD}$ . Considering one cycle which involves rising and falling transition of the output, the charge  $Q = C*V_{DD}$  is consumed for low to high transition. The same charge is passed to the ground in the high to low transition of the output. By assuming the frequency of the input signal as  $f_s$ , and the time period for the operation as T, the dynamic power is given by the equation 1.1:

$$P_{dynamic} = \frac{1}{T} \int_0^T i_{DD}(t) V_{DD} dt$$

(1.1)

Solving equation (1.1), we get

$$P_{dynamic} = CV_{DD}^2 f_s \tag{1.2}$$

The equation (1.2) can also be written as

$$P_{dynamic} = \alpha \, C V_{DD}^2 f_{ck} \tag{1.3}$$

Where  $\alpha$  is the activity factor for the node transition and  $f_{ck}$  is clock frequency.

# **1.5.2 Short Circuit Power Dissipation**

During the switching of the CMOS transistor circuit, a momentary phase is reached when both the transistors, viz. NMOS and PMOS turn on and a short circuit path for the current exists between the high and low power supply. This results in the glitch of short circuit current. Considering  $I_m$  as the average short circuit current, the short circuit power dissipation is specified by equation (1.4).

$$\mathbf{P}_{\mathrm{SC}} = \mathbf{I}_{\mathrm{m}}^* \mathbf{V}_{\mathrm{DD}} \tag{1.4}$$

The value of  $I_m$  for the symmetrical CMOS inverter is given by equation (1.5) as [8]

$$I_m = \frac{\beta}{12} \left( V_{DD} - 2V_{th} \right)^3 \frac{t_{rf}}{t_p}$$

(1.5)

Here  $V_{th}$  is the threshold voltage of both the MOSFETs,  $\beta$  is the current gain of MOSFET,  $t_{rf}$  is the rising and falling time period of the input signal and  $t_p$  as the pulse time period.

# 1.5.3 Static Leakage Power Dissipation

It is the power dissipation by the leakage current components present in the device when the transistor is in the off state. Considering n transistors in the circuits each having  $I_{off}$  as the off-state leakage current. The total static leakage power of the circuit is given by equation 1.6.

$$P_{static} = V_{DD} \sum_{i=1}^{n} I_{off_i}$$

(1.6)

# 1.5.3.1 Static Leakage Current

Figure 1.4 depicts the various leakage current components which are present in MOS devices.

Figure 1.4: MOS device leakage currents [12]

- I<sub>1</sub> represents the leakage current in a reverse-biased p-n junction

- I2 represents the subthreshold leakage current

- I<sub>3</sub> represents the gate-oxide leakage current

- I4 represents the hot-carrier injection current

I<sub>5</sub> signifies the Gate Induced Drain Leakage (GIDL) current

I<sub>6</sub> signifies the punch-through current.

The off-state leakage currents are mainly contributed by  $I_2$ ,  $I_5$  and  $I_6$ , whereas  $I_1$  and  $I_3$  take place in both OFF and ON states [12].

## i) Reverse biased p-n junction Current (I<sub>1</sub>)

The diode which is present between source/drain to the substrate will be normally reverse-biased which causes reverse current  $I_1$ . This current  $I_1$  can be attributed to the drift/diffusion of minority carriers near the depletion region edge and the electron-hole pair generation in the depletion region.

## ii) Sub-threshold Leakage Current (I<sub>2</sub>)

When the gate voltage is below  $V_{th}$  then the MOS device should be in an off state ideally. However, a small amount of current that flows between the source and drain, and is known as Sub-threshold Leakage Current (I<sub>2</sub>). This state of the MOS device is also called a weak inversion. In this state, the concentration of minority carriers is negligible and a whole voltage drop is observed across the reverse-biased junction. This results in a very little change in the electrostatic potential at the surface of the semiconductor towards the channel which produces a very small electric field. The drift current component is very small due to the mitigation of mobile carriers and the longitudinal electric field [12]. The sub-threshold current is contributed mainly by the diffusion mechanism.

# iii) Tunneling Gate Oxide Leakage Current (I<sub>3</sub>)

The continuous scaling of gate oxide causes enhancement in the field across the oxide. The high electric field coupled with low oxide thickness results in tunneling of electrons from the substrate to the gate and also from gate to substrate through the oxide layer. The tunneling involves Fowler–Nordheim (FN) tunneling and direct tunneling [13].

## iv) Hot Carriers Injection Current (I<sub>4</sub>)

The electric field is high near the Silicon–Silicon oxide interface (Si-SiO<sub>2</sub>). Due to this the electrons or holes have enough energy to jump the interface and penetrate the oxide layer. This phenomenon is called hot-carrier injection. The holes injection from Si to  $SiO_2$  is less prone than electrons [8] because the holes have higher effective mass.

#### v) Gate Induced Drain Leakage current (I<sub>5</sub>)

The Gate Induced Drain Leakage (GIDL) occurs when the drain is subjected to higher voltages by keeping the gate at ground potential. This results in the creation of a depletion region under the overlap of drain and gate. The tunneling of the electrons from the valence band to the conduction band creates the electron-hole pair in the region. These pairs are collected by substrate and drain. The band to band tunneling under the overlapped drain and gate region causes the GIDL current (I<sub>5</sub>). The GIDL current is directly proportional to drain voltage and inversely proportional to gate voltage [7].

#### vi) Punch through current (I<sub>6</sub>)

The nearness of drain and source terminal of MOSFET in short channel devices cause the extension of the depletion region into the channel. The distance between the depletion region boundaries reduces with a reduction in channel length at constant doping. With the rise in  $V_{ds}$ , reverse bias across the junctions increases and it pushes the junctions further near to each other. With the significant increase in  $V_{ds}$ , merging of these two depletion regions occurs and this is known as punch-through. Due to punch through current, the performance of small size MOS transistors heavily depends upon drain bias. The other effect which is very similar to the punch-through is Drain-Induced Barrier Lowering (DIBL) [7].

#### **1.6 DESIGNING FOR LOW POWER**

The semiconductor technology has to be scaled down to meet the challenges of future circuits to improve the performance of the system and to reduce the cost of the system. The scaled circuits will have a denser packing of transistors working at high

frequency. This approach will usually result in more power dissipation. The factors like supply voltage  $V_{DD}$  hence are to be scaled in the same proportion to reduce power dissipation. This supply voltage scaling will impact the working of the transistor if the threshold voltage of the device is not scaled in the same proportion to maintain the appropriate gate current drive [6]. The factors like size of the transistor, supply voltage, threshold voltage, etc. have an enormous impact on the power dissipation.

# **1.7 POWER MINIMIZATION TECHNIQUES**

Recently the semiconductor industry has adopted many approaches for facing the challenges of power reduction. Some of these approaches are as:

# **1.7.1 Supply Voltage Scaling**

It is the most effective approach for the reduction of power dissipation. With every new generation of scaling, the IC fabrication processing mechanism has to be revamped. This power reduction approach often requires detailed consideration of issues like the signal-to-noise ratio and supported circuit integration for low voltage operation.

#### **1.7.2 Reduction of Capacitance**

The capacitance also plays a vital role in the power dissipation of the circuits. The capacitance can be reduced by using the latest design process approaches to make transistors with techniques like SOI (Silicon on Insulator). The implementation of these processes requires a compatible fabrication facility and time to research & development for the upcoming concerns.

## 1.7.3 Better Design Techniques Employment

This approach consists of research in the design perspective of the circuits for the reduction of power dissipation. A better arrangement of the various component of the circuit will result in a significant reduction of power dissipation.

## **1.7.4 Better Power Management Approaches**

A better power management approach combining various approaches like device scaling, supply voltage scaling and a better choice of circuit architecture can provide the best solution for the power savings. All or some of these approaches can be effectively applied to obtain the optimal power-delay-area trade-off.

#### **1.8 MOORE'S LAW**

The scaling of the device dimension allows creating a high-performance system on the integrated circuit having minimum power consumption and occupying a very small area. Gordon Moore, co-founder of Intel, in 1965, had predicted about the scaling, that the number of transistors on a wafer in a given area will get doubled in every 18 months [3]. This law has been the motivating force behind the continuous reduction of device dimensions using scaling as shown in Figure 1.5.

Figure 1.5: Moore's law

The scaling process has taken the CMOS devices in the sub-nano regime. The basic device structure still is the same but the gate lengths have been decreased from a few mm in the 1970s to less than 10nm recently in the fabrication unit [2]. The gate oxide thicknesses have also been reduced in the same proportion.

## **1.9 MOSFET SCALING**

The semiconductor device technology is always aiming for the reduced size of the device. The process of reduction of the dimension of a MOSFET is known as scaling. Scaling maintains the same geometry as of the equivalent larger devices. It usually results in fast performance with more devices per unit area of the semiconductor. The channel length, width, doping density and oxide thickness are the major components on which the scaling is carried out. The scaling results in enhanced packaging density, operation speed and reduction in the cost of the IC [6]. Figure 1.6 shows the growing number of transistors on microprocessor ICs in the last 20 years.

Figure 1.6: The increasing number of transistors per chip with device technology [10]

With the continuous scaling over the years, at present, the scaling of various dimensions has reached its optimum values and a further reduction in the oxide thickness will dent the insulator operations in MOSFETs. Hence, the appropriate mechanism is required to maintain a low gate leakage current besides device scaling.

# **1.9.1 Constant Field Scaling**

Full scaling or constant field scaling is proposed by Dennard et al. [6]. In this scaling, a scaling factor 'K' is used to scale the dimension and voltage of the MOSFET, while sustaining the magnitude of the internal electric field in the horizontal and vertical direction as constant. This is achieved by scaling all the voltages in the same

proportion as device dimensions scaling. To maintain the constant electric field both  $V_{gs}$  (gate voltage) and  $V_{ds}$  (drain voltage) must be scaled by the same factor 'K' along with the t<sub>ox</sub> (gate oxide thickness) by scaling the channel length by the same factor K. The substrate doping concentration is increased by a factor of 'K' to reduce the depletion width in the same proportion of channel length. The constant field scaling results in reducing the power-delay product of a MOSFET, the total power remains constant by keeping the area of the chip constant.

### 1.9.2 Constant Voltage Scaling

One of the limitations of constant field scaling is that the semiconductor device width cannot be scaled aggressively in the weak inversion region. The largest portion of the available supply voltage is consumed while switching the device. On the other hand, in constant voltage scaling, the potential of the devices remains unchanged while the scaling of the device dimensions is done by a factor 'K'. This scaling results in an increase in the electric field and power dissipation. As the voltage remains constant in this scaling, the voltage compatibility is obtained with older circuit design methodologies [6]. The value of the threshold voltage will remain constant in this scaling but the power per device increases by a factor of 'K' which causes high power density per unit area. The substrate doping in this scaling also needs to be increased by a factor of 'K' to reduce the depletion width.

The constant voltage scaling results in an increase in an electric field with reduced dimensions. This phenomenon usually causes high leakage current, mobility degradation, low breakdown voltages and increased channel punch through, and hence, this type of scaling is generally not preferred.

## **1.9.3 Generalized Scaling**

In the generalized scaling, the dimension of the device and the voltage of the device are scaled by different factors. This scaling results in low power dissipation and efficient speed of operation.

## **1.9.4 Modern Scaling**

The threshold voltage and supply voltage are kept constant to maintain the balance between the off and on-current of the device. The high value of  $I_{on}$  and low value of  $I_{off}$  are more desirable to achieve high speed and low power for the semiconductor device. The threshold voltage is one of the key parameters to maintain the tradeoffs between speed and power. Modern scaling introduces the new doping profile like halo implants, new dielectric materials and strain engineering to increase mobility [14].

Table 1.1 shows the various types of scaling. The physical quantity before and after scaling is also mentioned in the Table.

| Parameter<br>Name       | Before<br>scaling | Constant Field<br>Scaling | Constant<br>Voltage<br>Scaling | Generalized<br>Scaling |

|-------------------------|-------------------|---------------------------|--------------------------------|------------------------|

| Channel Length          | L                 | 1/K                       | 1/K                            | 1/K                    |

| Channel Width           | W                 | 1/K                       | 1/K                            | 1/K                    |